扫一扫

关注中图网

官方微博

本类五星书更多>

-

>

全国计算机等级考试最新真考题库模拟考场及详解·二级MSOffice高级应用

-

>

决战行测5000题(言语理解与表达)

-

>

软件性能测试.分析与调优实践之路

-

>

第一行代码Android

-

>

JAVA持续交付

-

>

EXCEL最强教科书(完全版)(全彩印刷)

-

>

深度学习

买过本商品的人还买了

Python编程从入门到实践(第3版)

¥76.9¥109.8SRv6:可编程网络技术原理与实践

¥91.4¥149.8HCNA-WLAN学习指南

¥60.9¥99.8LoRa物联网通信技术

¥57.9¥79.0RISC-V架构与嵌入式开发快速入门

¥51.6¥79.0

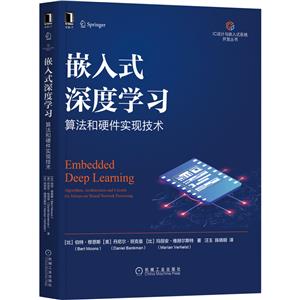

嵌入式深度学习:算法和硬件实现技术 版权信息

- ISBN:9787111688075

- 条形码:9787111688075 ; 978-7-111-68807-5

- 装帧:一般胶版纸

- 册数:暂无

- 重量:暂无

- 所属分类:>

嵌入式深度学习:算法和硬件实现技术 本书特色

详细介绍如何在应用层、算法层、硬件架构层和电路层进行设计和优化,以及跨层次的软硬件协同设计

嵌入式深度学习:算法和硬件实现技术 内容简介

本书介绍了实现嵌入式深度学习的算法和硬件实现技术。作者描述了应用、算法、电路级的协同设计方法,这些方法有助于实现降低深度学习算法计算成本的目标。这些技术的影响显示在四个用于嵌入式深度学习的硅原型中。

嵌入式深度学习:算法和硬件实现技术 目录

译者序

前言

致谢

缩写词

第1章 嵌入式深度神经网络 1

1.1 简介 1

1.2 机器学习 2

1.2.1 任务T 3

1.2.2 性能度量P 3

1.2.3 经验E 4

1.3 深度学习 4

1.3.1 深度前馈神经网络 6

1.3.2 卷积神经网络 8

1.3.3 循环神经网络 16

1.3.4 训练深度神经网络 18

1.4 嵌入式深度神经网络的挑战 25

1.5 本书创新点 27

参考文献 29

第2章 优化的层次级联处理 34

2.1 简介 34

2.2 层次级联系统 36

2.2.1 泛化的两级唤醒系统 36

2.2.2 层次化的代价、精度和召回率 37

2.2.3 层次化分类器的Roofline模型 40

2.2.4 优化的层次级联感知 42

2.3 概念的一般性证明 43

2.3.1 系统描述 43

2.3.2 输入统计 45

2.3.3 实验 46

2.3.4 本节小结 48

2.4 案例研究:基于CNN的层次化人脸识别 49

2.4.1 人脸识别的分层结构 49

2.4.2 层次化的代价、精度和召回率 51

2.4.3 优化的人脸识别分层结构 52

2.5 小结 55

参考文献 56

第3章 硬件–算法协同优化 58

3.1 简介 58

3.1.1 利用网络结构 59

3.1.2 增强并利用稀疏性 63

3.1.3 增强并利用容错性 64

3.2 低精度神经网络的能量增益 66

3.2.1 片外访存的能耗 67

3.2.2 硬件平台的一般性建模 68

3.3 测试时定点神经网络 69

3.3.1 分析和实验 70

3.3.2 量化对分类准确率的影响 70

3.3.3 稀疏FPNN的能耗 73

3.3.4 结果 75

3.3.5 讨论 76

3.4 训练时量化神经网络 77

3.4.1 训练QNN 78

3.4.2 QNN的能耗 81

3.4.3 实验 81

3.4.4 结果 84

3.4.5 讨论 88

3.5 聚类神经网络 88

3.6 小结 90

参考文献 91

第4章 近似计算的电路技术 95

4.1 近似计算范式简介 95

4.2 近似计算技术 98

4.2.1 容错分析与质量管理 98

4.2.2 近似电路 99

4.2.3 近似架构 100

4.2.4 近似软件 101

4.2.5 讨论 102

4.3 DVAFS:动态电压精度频率调节 102

4.3.1 DVAFS基础 102

4.3.2 DVAFS的容错识别 105

4.3.3 DVAFS的能量增益 106

4.4 DVAFS的性能分析 109

4.4.1 模块级的DVAFS 109

4.4.2 系统级的DVAFS 111

4.5 DVAFS实现的挑战 115

4.5.1 基础DVA(F)S模块的功能实现 115

4.5.2 基础DVA(F)S模块的物理实现 117

4.6 小结和讨论 118

参考文献 119

第5章 Envision:能耗可调节的稀疏卷积神经网络处理 122

5.1 神经网络加速 122

5.2 针对嵌入式CNN的二维MAC处理器架构 124

5.2.1 处理器数据通路 125

5.2.2 片上存储架构 128

5.2.3 利用网络稀疏性的硬件支持 130

5.2.4 通过定制化指令集实现高能效的灵活性 132

5.3 基于40nm CMOS的DVAS兼容的Envision处理器 133

5.3.1 RTL级的硬件支持 134

5.3.2 物理实现 135

5.3.3 测量结果 136

5.3.4 Envision V1回顾 143

5.4 基于28nm FD-SOI的DVAFS兼容的Envision处理器 144

5.4.1 RTL级硬件支持 146

5.4.2 物理实现 147

5.4.3 测量结果 147

5.4.4 Envision V2回顾 156

5.5 小结 157

参考文献 158

第6章 BinarEye: 常开的数字及混合信号二值神经网络处理 160

6.1 二值神经网络 160

6.1.1 简介 160

6.1.2 二值神经网络层 161

6.2 二值神经网络应用 165

6.3 可编程的输入到标签的加速器架构 167

6.3.1 256X:基础的BinaryNet计算架构 169

6.3.2 SX:灵活的DVAFS BinaryNet计算架构 178

6.4 MSBNN:混合信号的256X实现 182

6.4.1 开关电容神经元阵列 183

6.4.2 测量结果 184

6.4.3 模拟信号通路代价 188

6.5 BinarEye:数字的SX实现 189

6.5.1 全数字的二值神经元 189

6.5.2 物理实现 190

6.5.3 测量结果 190

6.5.4 BinarEye中的DVAFS 194

6.5.5 与*先进水平的对比 195

6.6 数字与模拟二值神经网络的实现对比 197

6.7 展望与未来工作 200

6.8 小结 202

参考文献 204

第7章 结论、贡献和未来工作 206

7.1 结论 207

7.2 未来工作的建议 210

参考文献 211

索引 212

前言

致谢

缩写词

第1章 嵌入式深度神经网络 1

1.1 简介 1

1.2 机器学习 2

1.2.1 任务T 3

1.2.2 性能度量P 3

1.2.3 经验E 4

1.3 深度学习 4

1.3.1 深度前馈神经网络 6

1.3.2 卷积神经网络 8

1.3.3 循环神经网络 16

1.3.4 训练深度神经网络 18

1.4 嵌入式深度神经网络的挑战 25

1.5 本书创新点 27

参考文献 29

第2章 优化的层次级联处理 34

2.1 简介 34

2.2 层次级联系统 36

2.2.1 泛化的两级唤醒系统 36

2.2.2 层次化的代价、精度和召回率 37

2.2.3 层次化分类器的Roofline模型 40

2.2.4 优化的层次级联感知 42

2.3 概念的一般性证明 43

2.3.1 系统描述 43

2.3.2 输入统计 45

2.3.3 实验 46

2.3.4 本节小结 48

2.4 案例研究:基于CNN的层次化人脸识别 49

2.4.1 人脸识别的分层结构 49

2.4.2 层次化的代价、精度和召回率 51

2.4.3 优化的人脸识别分层结构 52

2.5 小结 55

参考文献 56

第3章 硬件–算法协同优化 58

3.1 简介 58

3.1.1 利用网络结构 59

3.1.2 增强并利用稀疏性 63

3.1.3 增强并利用容错性 64

3.2 低精度神经网络的能量增益 66

3.2.1 片外访存的能耗 67

3.2.2 硬件平台的一般性建模 68

3.3 测试时定点神经网络 69

3.3.1 分析和实验 70

3.3.2 量化对分类准确率的影响 70

3.3.3 稀疏FPNN的能耗 73

3.3.4 结果 75

3.3.5 讨论 76

3.4 训练时量化神经网络 77

3.4.1 训练QNN 78

3.4.2 QNN的能耗 81

3.4.3 实验 81

3.4.4 结果 84

3.4.5 讨论 88

3.5 聚类神经网络 88

3.6 小结 90

参考文献 91

第4章 近似计算的电路技术 95

4.1 近似计算范式简介 95

4.2 近似计算技术 98

4.2.1 容错分析与质量管理 98

4.2.2 近似电路 99

4.2.3 近似架构 100

4.2.4 近似软件 101

4.2.5 讨论 102

4.3 DVAFS:动态电压精度频率调节 102

4.3.1 DVAFS基础 102

4.3.2 DVAFS的容错识别 105

4.3.3 DVAFS的能量增益 106

4.4 DVAFS的性能分析 109

4.4.1 模块级的DVAFS 109

4.4.2 系统级的DVAFS 111

4.5 DVAFS实现的挑战 115

4.5.1 基础DVA(F)S模块的功能实现 115

4.5.2 基础DVA(F)S模块的物理实现 117

4.6 小结和讨论 118

参考文献 119

第5章 Envision:能耗可调节的稀疏卷积神经网络处理 122

5.1 神经网络加速 122

5.2 针对嵌入式CNN的二维MAC处理器架构 124

5.2.1 处理器数据通路 125

5.2.2 片上存储架构 128

5.2.3 利用网络稀疏性的硬件支持 130

5.2.4 通过定制化指令集实现高能效的灵活性 132

5.3 基于40nm CMOS的DVAS兼容的Envision处理器 133

5.3.1 RTL级的硬件支持 134

5.3.2 物理实现 135

5.3.3 测量结果 136

5.3.4 Envision V1回顾 143

5.4 基于28nm FD-SOI的DVAFS兼容的Envision处理器 144

5.4.1 RTL级硬件支持 146

5.4.2 物理实现 147

5.4.3 测量结果 147

5.4.4 Envision V2回顾 156

5.5 小结 157

参考文献 158

第6章 BinarEye: 常开的数字及混合信号二值神经网络处理 160

6.1 二值神经网络 160

6.1.1 简介 160

6.1.2 二值神经网络层 161

6.2 二值神经网络应用 165

6.3 可编程的输入到标签的加速器架构 167

6.3.1 256X:基础的BinaryNet计算架构 169

6.3.2 SX:灵活的DVAFS BinaryNet计算架构 178

6.4 MSBNN:混合信号的256X实现 182

6.4.1 开关电容神经元阵列 183

6.4.2 测量结果 184

6.4.3 模拟信号通路代价 188

6.5 BinarEye:数字的SX实现 189

6.5.1 全数字的二值神经元 189

6.5.2 物理实现 190

6.5.3 测量结果 190

6.5.4 BinarEye中的DVAFS 194

6.5.5 与*先进水平的对比 195

6.6 数字与模拟二值神经网络的实现对比 197

6.7 展望与未来工作 200

6.8 小结 202

参考文献 204

第7章 结论、贡献和未来工作 206

7.1 结论 207

7.2 未来工作的建议 210

参考文献 211

索引 212

展开全部

书友推荐

- >

史学评论

史学评论

¥14.4¥42.0 - >

上帝之肋:男人的真实旅程

上帝之肋:男人的真实旅程

¥20.2¥35.0 - >

中国历史的瞬间

中国历史的瞬间

¥16.7¥38.0 - >

烟与镜

烟与镜

¥18.3¥48.0 - >

有舍有得是人生

有舍有得是人生

¥25.7¥45.0 - >

名家带你读鲁迅:朝花夕拾

名家带你读鲁迅:朝花夕拾

¥10.5¥21.0 - >

回忆爱玛侬

回忆爱玛侬

¥24.0¥32.8 - >

龙榆生:词曲概论/大家小书

龙榆生:词曲概论/大家小书

¥8.7¥24.0

本类畅销

-

这就是ChatGPT

¥41.9¥59.8 -

机器学习

¥47.4¥108 -

深度学习导论

¥24.5¥49 -

正版图书携程人工智能实践

¥51.1¥109 -

TensorFlow实战

¥26.3¥79 -

做好课题申报:AI辅助申请书写作

¥48.9¥69.8

浏览历史

数量经济学前沿文献导读

¥69.4¥95.0引力场中的量子信息(英文)

¥79.4¥128.0物理云学习——高考物理极速通关手册

¥45.0¥69.8爆破地震波信号分析理论与技术

¥71.3¥99.0PH模型在城轨交通车站系统中的应用

¥50.0¥68.0