-

>

湖南省志(1978-2002)?铁路志

-

>

公路车宝典(ZINN的公路车维修与保养秘籍)

-

>

晶体管电路设计(下)

-

>

基于个性化设计策略的智能交通系统关键技术

-

>

德国克虏伯与晚清火:贸易与仿制模式下的技术转移

-

>

花样百出:贵州少数民族图案填色

-

>

识木:全球220种木材图鉴

从算法到电路:数字芯片算法的电路实现

¥83.3¥119.0UNIX环境高级编程(第3版)

¥164.9¥229.0无线光通信中的空间光-光纤耦合技术

¥77.8¥108.0新概念模拟电路 中 频率特性和滤波器

¥111.9¥159.8Python编程从入门到实践(第3版)

¥76.9¥109.8

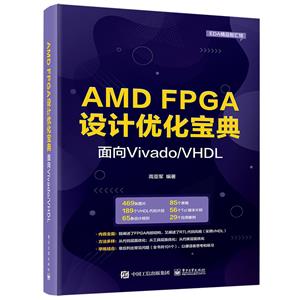

AMD FPGA设计优化宝典:面向Vivado/VHDL 版权信息

- ISBN:9787121450983

- 条形码:9787121450983 ; 978-7-121-45098-3

- 装帧:平塑

- 册数:暂无

- 重量:暂无

- 所属分类:>>

AMD FPGA设计优化宝典:面向Vivado/VHDL 本书特色

内容全面:既阐述了FPGA内部结构,又阐述了RTL代码风格(采用VHDL语言)方法多样:从代码层面优化;从工具层面优化;从约束层面优化学练结合:章后列出常见问题(全书共101个),以便读者思考和练习内容全面:既阐述了FPGA内部结构,又阐述了RTL代码风格(采用VHDL语言)方法多样:从代码层面优化;从工具层面优化;从约束层面优化学练结合:章后列出常见问题(全书共101个),以便读者思考和练习

AMD FPGA设计优化宝典:面向Vivado/VHDL 内容简介

本书以Xilinx公司(目前已被AMD公司收购)的7系列FPGA、UltraScale/UltraScale+ FPGA和Versal ACAP内部架构为基础,介绍与之匹配的RTL代码的风格(采用VHDL语言)和基于Vivado的设计分析方法。全书共10章,包括时钟网络、组合逻辑、触发器、移位寄存器、存储器、乘加运算单元和状态机的代码风格和优化方法,也包含扇出和布线拥塞的优化方法。本书可供电子工程领域的本科生和研究生学习参考,也可供FPGA工程师和自学者参考使用。

AMD FPGA设计优化宝典:面向Vivado/VHDL 目录

1.1 芯片架构的演变 1

1.2 设计方法的演变 15

1.3 面临的挑战 20

1.4 四大基本原则 22

1.4.1 硬件原则 23

1.4.2 同步原则 24

1.4.3 流水原则 25

1.4.4 面积与速度的平衡与互换原则 27

1.5 性能指标 29

1.6 思考空间 31

第2章 优化时钟网络 32

2.1 时钟资源 32

2.1.1 7系列FPGA中的时钟资源 32

2.1.2 UlatraScale/UltraScale FPGA中的时钟资源 42

2.1.3 Versal ACAP中的时钟资源 47

2.2 时钟偏移 52

2.3 时钟抖动 64

2.4 安全的时钟启动方式 71

2.5 时钟规划 75

2.6 创建输出时钟 79

2.7 思考空间 80

第3章 优化组合逻辑 81

3.1 组合逻辑资源 81

3.2 译码器与编码器 82

3.2.1 译码器代码风格 82

3.2.2 编码器代码风格 93

3.3 多路复用器与多路解复用器 104

3.3.1 多路复用器代码风格 104

3.3.2 多路解复用器代码风格 117

3.4 加法器与累加器 119

3.4.1 加法器代码风格 119

3.4.2 累加器代码风格 134

3.5 其他组合逻辑电路 149

3.5.1 移位器代码风格 149

3.5.2 比较器代码风格 153

3.5.3 奇偶校验电路代码风格 166

3.5.4 二进制码与格雷码互转电路代码风格 167

3.6 避免组合逻辑环路 170

3.7 思考空间 171

第4章 优化触发器 172

4.1 触发器资源 172

4.1.1 7系列FPGA中的触发器资源 172

4.1.2 UltraScale/UltraScale FPGA中的触发器资源 174

4.1.3 Versal ACAP中的触发器资源 175

4.2 建立时间和保持时间 179

4.3 亚稳态 181

4.4 控制集 184

4.5 复位信号的代码风格 189

4.5.1 异步复位还是同步复位 189

4.5.2 全局复位还是局部复位 192

4.5.3 是否需要上电复位 195

4.6 同步边沿检测电路代码风格 199

4.7 串并互转电路代码风格 201

4.8 避免意外生成的锁存器 206

4.9 思考空间 209

第5章 优化移位寄存器 211

5.1 移位寄存器资源 211

5.1.1 7系列FPGA中的移位寄存器资源 211

5.1.2 UltraScale/UltraScale FPGA中的移位寄存器资源 212

5.1.3 Versal ACAP中的移位寄存器资源 212

5.2 移位寄存器的代码风格 216

5.3 移位寄存器的应用场景 227

5.4 管理时序路径上的移位寄存器 228

5.5 思考空间 232

第6章 优化存储器 234

6.1 存储器资源 234

6.1.1 分布式RAM 234

6.1.2 BRAM 235

6.1.3 UltraRAM 242

6.2 单端口RAM代码风格 246

6.3 简单双端口RAM代码风格 266

6.4 真双端口RAM代码风格 276

6.5 RAM的初始化与ROM代码风格 284

6.6 同步FIFO代码风格 287

6.7 异步FIFO代码风格 301

6.8 平衡BlockRAM的功耗与性能 310

6.9 异构RAM 312

6.10 以IP方式使用RAM和FIFO 312

6.11 以XPM方式使用RAM或FIFO 319

6.12 管理时序路径上的BRAM和UltraRAM 322

6.13 思考空间 328

第7章 优化乘加运算单元 329

7.1 乘加器资源 329

7.1.1 7系列FPGA中的乘加器资源 329

7.1.2 UltraScale/UltraScale FPGA中的乘加器资源 332

7.1.3 Versal ACAP中的乘加器资源 332

7.2 以乘法为核心运算的代码风格 335

7.3 复数乘法运算代码风格 363

7.4 向量内积代码风格 378

7.5 以加法为核心运算的电路结构 380

7.6 管理时序路径上的乘加器 386

7.7 思考空间 387

第8章 优化状态机 388

8.1 基本概念 388

8.2 状态机代码风格 390

8.3 状态编码方式 410

8.4 基于ROM的控制器 413

8.5 思考空间 416

第9章 优化扇出 417

9.1 生成扇出报告 417

9.2 利用设计流程降低扇出 419

9.3 利用约束降低扇出 421

9.4 从代码层面降低扇出 424

9.5 改善扇出的正确流程 424

9.6 思考空间 425

第10章 优化布线拥塞 426

10.1 布线拥塞的三种类型 426

10.2 利用设计流程改善布线拥塞 428

10.3 利用约束缓解布线拥塞 429

10.4 从代码层面降低布线拥塞程度 430

10.5 缓解布线拥塞的正确流程 430

10.6 思考空间 432

AMD FPGA设计优化宝典:面向Vivado/VHDL 作者简介

高亚军,FPGA技术分享者,设计优化和时序收敛专家,Vivado工具使用专家,数字信号处理专家,现任Xilinx资深战略应用工程师,多年来使用Xilinx FPGA实现数字信号处理算法,对Xilinx FPGA器件架构、开发工具Vivado/Vitis HLS/Model Composer及其设计理念有深厚的理论和实战经验。

- >

企鹅口袋书系列·伟大的思想20:论自然选择(英汉双语)

企鹅口袋书系列·伟大的思想20:论自然选择(英汉双语)

¥6.3¥14.0 - >

朝闻道

朝闻道

¥8.8¥23.8 - >

罗曼·罗兰读书随笔-精装

罗曼·罗兰读书随笔-精装

¥20.3¥58.0 - >

推拿

推拿

¥12.2¥32.0 - >

上帝之肋:男人的真实旅程

上帝之肋:男人的真实旅程

¥19.3¥35.0 - >

巴金-再思录

巴金-再思录

¥14.7¥46.0 - >

中国历史的瞬间

中国历史的瞬间

¥16.7¥38.0 - >

罗庸西南联大授课录

罗庸西南联大授课录

¥13.8¥32.0

-

基于融合表征的多视图学习方法

¥23¥30 -

ANSYS电磁兼容仿真与场景应用案例实战

¥81.8¥109 -

业余无线电通信 第五版

¥62.6¥79 -

现代微波技术基础

¥14.5¥21 -

4.23文创礼盒A款--“作家言我精神状态”

¥42.3¥206 -

4.23文创礼盒B款--“作家言我精神状态”

¥42.3¥206